## On the effect of SOI substrate in silicon nitride resistance switching MIS structures

A.E. Mavropoulis<sup>a</sup><sup>\*</sup>, N. Vasileiadis<sup>a,b</sup>, T.Tsiamis<sup>a</sup>, C. Theodorou<sup>c</sup>, L. Sygellou<sup>d</sup>, P. Normand<sup>a</sup>, G. Ch. Sirakoulis<sup>b</sup>, P. Dimitrakis<sup>a,\*</sup>

<sup>a</sup> Institute of Nanoscience and Nanotechnology, NCSR "Demokritos", Ag. Paraskevi 15341, Greece

<sup>b</sup> Department of Electrical and Computer Engineering, Democritus University of Thrace, Xanthi 67100, Greece

<sup>c</sup> Univ. Grenoble Alpes, Univ. Savoie Mont Blanc, CNRS, Grenoble INP, IMEP-LAHC, 38000 Grenoble, France

<sup>d</sup> Institute of Chemical Engineering Sciences, FORTH/ ICE-HT, Patras 26504,

Greece

Several resistive memory technologies (RRAMs) are prominent, but few are fulfilling the requirements for CMOS integration and meet the commercialization standards. SiN<sub>x</sub> was found to exhibit competitive resistance switching (RS) properties and attractive SiN-based RRAM devices have been recently demonstrated [1-3]. In the majority of the publications, the RS SiN<sub>x</sub> structures are metal-insulator-semiconductor (MIS), meaning that the bottom electrode was  $n^{++}$  Si. In this work, the fabrication and electrical characterization of a fully compatible CMOS process on SOI substrate of 1R silicon SiN-based resistance switching MIS devices is presented. The RS characteristics are compared with the same devices previously fabricated on bulk silicon. The scope of this work is to benchmark the use of thin SOI film as bottom electrode compared to bulk Si substrates in single MIS RS cells (1R) utilizing low-frequency noise, DC and AC measurements.

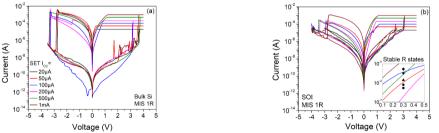

Typical round sweep I-V curves are presented in Fig. 1, where the current switching is evident due to the formation (+eV, SET)/ destroy (-eV, RESET) of a conductive filament made of nitrogen vacancies. The series resistance of the bottom electrode was found to be higher on SOI compared to Si wafer, while the SOI substrate devices exhibited self-compliance characteristics as revealed by *I*-V voltage sweeps and AC impedance measurements. Device-to-device variability of SET and RESET voltages suggest better uniformity for SOI substrates. Low-frequency noise spectral analysis indicated that there is no additional group of characteristic traps related to the SOI substrate.

Figure 1: I-V switching characteristics at different I<sub>CC</sub> for a) bulk Si substrate, b) SOI substrate 1R cells. c) SET/RESET voltage statistics.

## Acknowledgements

This work was supported in part by the research projects "3D-TOPOS" (MIS 5131411)

## References

- [1] N. Vasileiadis, et al., IEEE Trans. on Nanotechnology 20 (2021): 356-364

- [2] N. Vasileiadis, et al., Materials 2021, 14, 5223

- [3] N. Vasileiadis, et al., Chaos, Solitons & Fractals 153 (2021): 111533

<sup>\*</sup> a.mavropoulis@inn.demokritos.gr